DESIGN VERIFICATION

A Hawk-Eyed Methodology to Bug Free Silicon

Silicon defects form a costly pill for any semiconductor product company and smartly identifying these early on in the product life cycle is a silver bullet. Murphy’s law states that “Anything that can go wrong will go wrong”, hence the Design Verification Solutions are to be state-of-the-art in nature and should be carefully crafted to perceive the hidden bugs.

The Design Verification business unit within Simask believes in working towards covering all the functional, code coverage while continuously improvising the IP, Sub-System and System Level Verification Environment. Our experienced team has a robust verification environment and our unique verification methodologies can aim at achieving zero defect silicon.

We provide support in the following areas.

• Experience of handling multimillion gate designs in Wireless, Automotive, Connectivity, Consumer Applications, Medical, IoT domains.

• Full Chip/IP/Subsystem Verification Architecture development, Test Bench development and Functional verification.

• High Speed IP/Subsystem Verification Architecture development, Test Bench development and Functional verification (Processors such as ARM, MIPS etc)

• Full Chip Validation on parameters like latency, throughput, performance

• Power Aware functional verification

• Verification Flow and methodology support

• Verification IP development and support.

• Functional verification signoff (code coverage, functional coverage, formal verification, assertion, Gate-level simulation)

• Emulation/Prototyping support and system/flow setup.

Verification and Emulation of an Access Network Processor SoC

Verification and Emulation of an Access Network Processor SoC- Complete ownership of SoC Verification

- Designed a holistic phase-by-phase testing approach to evaluate the SoC and FW performance.

- Designed Layered Verification environment in SV, UVM and system models written in C.

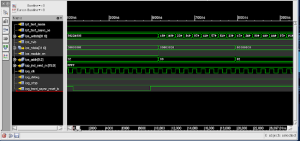

- Designed synthesised driver/monitor so that the same environment can be used for emulation( PALLADIUM).

- Closely interacted with System Architecture and Firmware team

- Verification of x86 Fusion Processor.

- Complete ownership of SoC Verification

- Integration and bring up of IPs

- Running Regressions and Debugging of Signatures.

- Bug tracking and closing.

- Verification of Embedded DFx Interface (EXI)

- Development of Verification Environment for PRIMARY to JTAG Interface in OVM.

- Performance monitoring of the system.

- Implementation of Scoreboard across the interfaces.

- Close interaction with System Architecture and Design team

- Define functional coverage and Development of Test Scenarios and Function Coverage

- Automotive Micro controller Validation

- System Level Validation of Power domains.

- Develop the power domain validation plan and identify the scenarios where system can halt due to design issues.

- Develop test scenarios in ARM assembly level , RTL Simulations.

- Formal Verification for equivalence check

- ECO implementations and validations

- Script based assertion development for connectivity checks.

- Verification of Domain Specific Abstract Core

- Complete ownership of IP and SoC Verification

- Designed a holistic phase-by-phase testing approach to evaluate the SoC and FW performance.

- Designed Layered Verification environment in SV and migrated the verification environment to OVM

- SilVERBullet™ Verification Methodology Frame Work for Bug Free Silicon